最早的“大脑”:从真空管到晶体管

1940年代,世界上之一台通用电子计算机ENIAC用一万八千支真空管充当开关,体积占满整个房间,耗电量足以让附近小镇灯光暗淡。 自问:为什么真空管会被淘汰? 自答:真空管易碎、发热巨大、寿命短,于是1947年贝尔实验室发明的晶体管迅速取而代之,体积缩小百倍,可靠性提升千倍,为CPU的微型化奠定物理基础。

集成电路革命:把一整个房间装进指甲盖

1958年,德州仪器的杰克·基尔比把多个晶体管、电阻、电容蚀刻在同一块硅片上,之一块集成电路诞生。 自问:这带来了什么质变? 自答: - 集成度指数级上升:从SSI(小规模)到MSI、LSI、VLSI,再到今天的ULSI,数十亿晶体管轻松塞进指甲盖。 - 成本雪崩式下降:1960年代一颗晶体管约1美元,如今同样价格可买数千万颗。 - 性能与功耗双优化:信号路径缩短,速度提升,能耗降低。

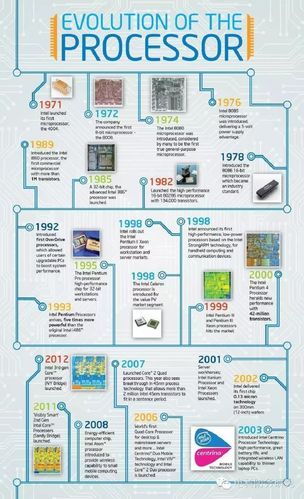

微处理器元年:Intel 4004开启个人计算时代

1971年,Intel为日本Busicom计算器设计的4位4004芯片意外成为之一颗商用微处理器,主频740kHz,集成2300个晶体管。 自问:它为何被称为“元年”? 自答: - 首次把CPU、寄存器、控制单元整合到单芯片,计算机从机房走向桌面。 - 指令集可编程,软件生态开始萌芽。 - 催生摩尔定律:晶体管数量每18~24个月翻倍,成为行业心跳。

16位到32位:性能与寻址空间的飞跃

1978年Intel 8086(16位)与1985年80386(32位)相继问世,后者把寻址空间从64KB扩展到4GB,图形界面与多任务成为可能。 自问:32位为何够用20年? 自答: - 4GB内存天花板直到2000年代才被消费级应用触及。 - 向后兼容的x86指令集让软件资产得以延续,形成强大的生态护城河。

64位与多核:突破频率墙的新思路

2003年AMD抢先发布Opteron 64,把x86扩展到64位;随后Intel推出Core 2 Duo,正式开启多核竞赛。 自问:频率为何止步4GHz左右? 自答: - 功耗墙:频率再提升,发热呈指数级增长,散热成本失控。 - 指令级并行度见顶:流水线深度与乱序执行优化空间缩小。 多核成为唯一可行路线:从双核、四核到今天的64核128线程,软件并行化成为新瓶颈。

移动与低功耗:ARM的逆袭

1985年诞生的ARM架构采用RISC精简指令集,以低功耗、高效率横扫手机、平板、物联网。 自问:ARM为何能在移动端打败x86? 自答: - 指令集简洁,解码电路小,功耗天然低。 - IP授权模式让苹果、高通、三星可定制SoC,快速迭代。 - 异构计算:大核+小核+GPU+NPU协同,动态调整性能与能耗。

异构与专用芯片:CPU不再是唯一主角

现代处理器把CPU、GPU、ISP、NPU、TPU封装进同一颗SoC,各司其职。 自问:CPU会被取代吗? 自答: - 通用性仍是CPU不可替代的优势,操作系统、复杂逻辑离不开它。 - 但重算力场景(AI训练、图形渲染)由专用芯片接管,CPU退居“调度者”角色。

量子与光计算:下一个50年

IBM、Google已实现百量级量子比特,光芯片实验室原型带宽达Tbps级。 自问:它们何时进入家用? 自答: - 量子纠错与室温运行仍是难题,预计2035年后先用于云端超算。 - 光计算短期聚焦数据中心互连,CPU+光I/O混合封装或成过渡方案。

如何看懂CPU型号?一张速查表

Intel:i3入门、i5主流、i7高性能、i9极致;后缀K可超频,H标压,U低压。 AMD:Ryzen 3/5/7/9对应同上;后缀X高频,G带核显。 ARM:Cortex-A78大核、A55小核,数字越大越新。

选购CPU的五个关键指标

- 核心/线程:视频渲染、虚拟机需求高,选12核以上。

- 主频与IPC:游戏更吃单核性能,IPC高比单纯高主频更重要。

- 缓存容量:L3越大,数据命中率越高,帧率越稳。

- TDP与散热:65W适合静音小机箱,125W需搭配240mm以上水冷。

- 平台生命周期:AM5插槽承诺用到2025+,升级空间大。

未来展望:Chiplet与3D封装

AMD Ryzen 7000系列率先采用Chiplet小芯片+3D V-Cache,把缓存堆叠到96MB,游戏性能暴涨。 自问:Chiplet为何是趋势? 自答: - 降低大芯片良率成本,缺陷单元可单独替换。 - 灵活组合不同工艺节点:5nm计算核心配6nm I/O Die,平衡性能与成本。 - 标准化接口(如UCIe)让多厂商IP像乐高一样拼接,加速创新。

评论列表