半导体芯片制造工艺有哪些步骤?

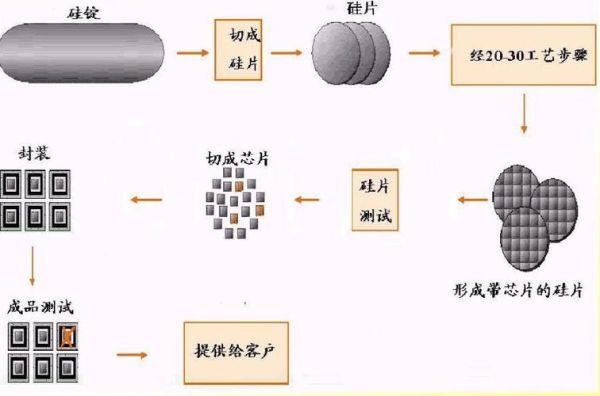

芯片从一粒沙子到最终封装,需要经历数百道精密工序。下面把最核心的流程拆成七个阶段,自问自答,帮你快速看懂。

(图片来源 *** ,侵删)

1. 硅片制备:为什么硅能成为芯片“地基”?

硅的四价共价键结构让它在常温下既稳定又能通过掺杂轻松改变导电性。流程:

- 石英砂→电弧炉冶炼→冶金级硅(纯度98%)

- 西门子法提纯→电子级多晶硅(纯度99.999999999%)

- 直拉单晶炉→单晶硅棒→线锯切片→抛光硅片

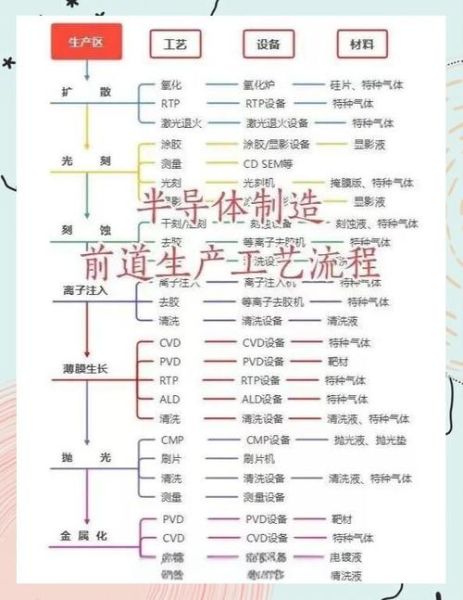

2. 氧化与光刻:怎样把电路图案“复印”到硅片?

先在硅片表面长一层二氧化硅绝缘层,再涂光刻胶,用紫外光透过掩膜版曝光。关键细节:

- 曝光波长越短,线宽越细:DUV 193 nm、EUV 13.5 nm

- 浸没式光刻用水作介质,提高数值孔径NA

- 显影后留下的胶图形就是后续刻蚀的“模板”

3. 刻蚀与离子注入:如何挖出晶体管沟道并精准掺杂?

刻蚀分干法(等离子体)与湿法(化学药液),先进制程几乎全用干法。离子注入:

- 硼(B)做P型,磷(P)做N型

- 能量决定注入深度,剂量决定浓度

- 退火修复晶格损伤并激活杂质

4. 薄膜沉积:怎样在三维结构中铺设导线与绝缘层?

分为CVD、PVD、ALD三大类:

- CVD:高温沉积多晶硅、氮化硅

- PVD:溅射铜、铝金属层

- ALD:原子层沉积高κ介质,厚度控制到埃级

5. 化学机械抛光(CMP):为何必须“磨平”才能继续堆叠?

多层金属布线需要每层都绝对平坦,否则光刻失焦。CMP用研磨液+研磨垫把高低差降到纳米级。

(图片来源 *** ,侵删)

6. 金属互连:铜为何取代铝?

铜电阻率1.68 µΩ·cm,铝为2.65 µΩ·cm,降低RC延迟。但铜易扩散,需先沉积Ta/TaN阻挡层,再电镀填充。

7. 测试与封装:怎么确保每颗芯片都合格?

流程:

- 晶圆测试(CP):探针台电性筛选

- 激光修调:修复冗余存储单元

- 切割→贴片→引线键合或倒装焊

- 塑封→终测→打码→出货

如何选择半导体材料?

选材料就是在性能、成本、工艺兼容性之间找平衡。下面用问答形式拆解。

1. 数字芯片为何仍死守硅?

硅的天然氧化层SiO₂质量极佳,界面缺陷密度低,配合成熟的CMOS工艺,能把晶体管尺寸缩到3 nm以下。其他材料要么氧化层不稳定,要么成本爆炸。

2. 射频前端为何拥抱GaAs与GaN?

关键指标:

(图片来源 *** ,侵删)

- 电子迁移率:GaAs 8500 cm²/V·s,硅仅1350

- 击穿场强:GaN 3.3 MV/cm,是硅的十倍

- 结果:GaAs做低噪声放大器,GaN做5G基站功放,效率提升20%以上

3. 功率器件为何青睐SiC?

电动车逆变器用SiC MOSFET,可把开关损耗降低70%,整车续航增加5%~10%。缺点是衬底贵,一片6英寸SiC晶圆价格是硅的5倍。

4. 光电芯片为何离不开InP?

光纤通信波长1.31 µm与1.55 µm,InP的直接带隙正好匹配,能高效发光。硅是间接带隙,发光效率低五个数量级。

5. 二维材料会是终极答案吗?

石墨烯、MoS₂等迁移率极高,但:

- 大面积单晶生长尚未突破

- 与现有工艺线兼容性差

- 目前仅用于实验室级柔性传感器

如何根据应用场景快速选材?

| 场景 | 首选材料 | 核心优势 |

|---|---|---|

| CPU/GPU | Si FinFET/GAA | 尺寸微缩、成本低 |

| 5G毫米波PA | GaN HEMT | 高功率密度 |

| 车载OBC | SiC MOSFET | 高温、高压、高频 |

| 激光雷达 | InGaAs/InP | 1550 nm人眼安全 |

| 柔性显示 | IGZO | 低温工艺、透明 |

未来趋势:材料与工艺的协同进化

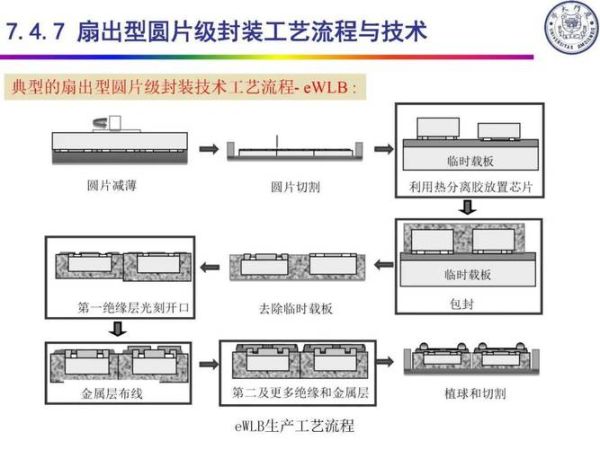

随着摩尔定律放缓,行业转向“More than Moore”:

- 硅基异质集成:把GaN、SiC、InP通过晶圆键合堆到硅衬底上

- 先进封装:Chiplet+TSV实现材料级混搭,不必所有功能都缩到一颗die

- 新型互连:用石墨烯或碳纳米管替代铜,降低RC延迟

一句话总结:选材料不是单点突破,而是系统级权衡。谁能把材料、器件、工艺、封装、测试全链路打通,谁就能在下一代半导体竞赛中领先。

评论列表